VHDL for FPGA Design/T Flip Flop

Jump to navigation

Jump to search

Synchronous Positive edge T Flip-Flop with Reset and Clock enable

[edit | edit source]

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity t_trigger is

port (T,Reset,CLK,CLK_enable: in std_logic;

Q: out std_logic);

end t_trigger;

architecture beh_t_trigger of t_trigger is

begin

process (Reset,CLK)

variable temp: std_logic;

begin

if (rising_edge(CLK)) then --sometimes you need to include a package for rising_edge, you can use CLK'EVENT AND CLK = '1' instead

if Reset='1' then

temp := '0';

elsif CLK_enable ='1' then

temp := T xor temp;

end if;

end if;

Q <= temp;

end process;

end beh_t_trigger;

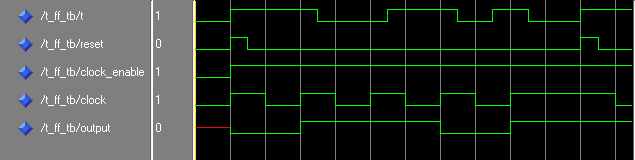

Simulation Results

[edit | edit source]

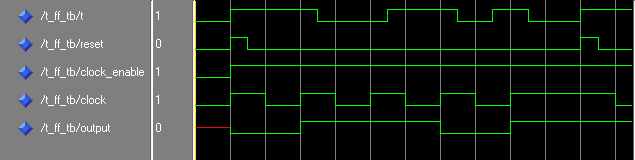

Generated Symbol

[edit | edit source] File:T FF SCH F.png