Practical Electronics/Flip-flops

A flip-flop is a circuit that exists in one of two states and so can store information. A simple flip-flop can be defined in terms of two NAND logic gates. Flip-flops are non-linear circuits, meaning the output from one of its gates is fed 'back' to be processed with the input signal. Because flip-flops operate on an input signal mixed with this previous output signal their own outputs are dependent upon their previous state.

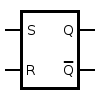

A flip flop (F/F) is a device made out of digital gates that uses feedback to store the state (1 or 0) of its input(s). Flip Flops are frequently used to latch input data. Meaning that flip flop 'remembers' its binary data until it is told to 'forget' it. All flip flops have at least one output labeled Q. Frequently they have a compliment labeled/Q. The 4 basic flip flops are RS, D, Toggle and JK flip flop

Types

[edit | edit source]Basic Configuration

[edit | edit source]Configuration Mathematical Expression Truth Table

Q = R + Q_

Q_ = S + QSR QQ 00 XX 01 01 10 10 11 00

Q = R . Q_

Q_ = S . QSR QQ 00 00 01 01 10 10 11 XX

RS Flip Flops

[edit | edit source]The fundamental latch is the simple SR flip-flop , where S and R stand for set and reset respectively. It can be constructed from a pair of cross-coupled NOR logic gates. The stored bit is present on the output marked Q.

Normally, in storage mode, the S and R inputs are both low, and feedback maintains the Q and Q outputs in a constant state, with Q the complement of Q. If S (Set) is pulsed high while R is held low, then the Q output is forced high, and stays high even after S returns low; similarly, if R (Reset) is pulsed high while S is held low, then the Q output is forced low and stays low even after R returns low.

| SR Flip-Flop operation [1] | |||||||

|---|---|---|---|---|---|---|---|

| Characteristic table | Excitation table | ||||||

| S | R | Action | Q(t) | Q(t+1) | S | R | Action |

| 0 | 0 | Keep state | 0 | 0 | 0 | X | No change |

| 0 | 1 | Q = 0 | 0 | 1 | 1 | 0 | Set |

| 1 | 0 | Q = 1 | 1 | 0 | 0 | 1 | Reset |

| 1 | 1 | Unstable combination, |

1 | 1 | X | 0 | No change |

('X' denotes a Don't care condition; meaning the signal is irrelevant)

D Flip Flops

[edit | edit source]The Q output always takes on the state of the D input at the moment of a rising clock edge. (or falling edge if the clock input is active low)[2] It is called the D flip-flop for this reason, since the output takes the value of the D input or Data input, and Delays it by one clock count. The D flip-flop can be interpreted as a primitive memory cell, zero-order hold, or delay line.

Truth table:

Clock D Q Qprev Rising edge 0 0 X Rising edge 1 1 X Non-Rising X Qprev

('X' denotes a Don't care condition, meaning the signal is irrelevant)

These flip flops are very useful, as they form the basis for shift registers, which are an essential part of many electronic devices. The advantage of the D flip-flop over the D-type latch is that it "captures" the signal at the moment the clock goes high, and subsequent changes of the data line do not influence Q until the next rising clock edge. An exception is that some flip-flops have a 'reset' signal input, which will reset Q (to zero), and may be either asynchronous or synchronous with the clock.

The above circuit shifts the contents of the register to the right, one bit position on each active transition of the clock. The input X is shifted into the leftmost bit position.

Toggle Flip Flops

[edit | edit source]If the T input is high, the T flip-flop changes state ("toggles") whenever the clock input is strobed. If the T input is low, the flip-flop holds the previous value. This behavior is described by the characteristic equation:

- (or, without benefit of the XOR operator, the equivalent: )

and can be described in a truth table:

| T Flip-Flop operation [1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| Characteristic table | Excitation table | |||||||

| Comment | Comment | |||||||

| 0 | 0 | 0 | hold state(no clk) | 0 | 0 | 0 | No change | |

| 0 | 1 | 1 | hold state(no clk) | 1 | 1 | 0 | No change | |

| 1 | 0 | 1 | toggle | 0 | 1 | 1 | Complement | |

| 1 | 1 | 0 | toggle | 1 | 0 | 1 | Complement | |

When T is held high, the toggle flip-flop divides the clock frequency by two; that is if clock frequency is 4 MHz, the output frequency obtained from the flip-flop will be 2 MHz. This 'divide by' feature has application in various types of digital counters. A T flip-flop can also be built using a JK flip-flop (J & K pins are connected together and act as T) or D flip-flop (T input and Qprevious are connected to the D input through an XOR gate).

JK Flip Flops

[edit | edit source]JK flip flop has 2 inputs labeled J and K, with a CLK input (marked by a triangle) which is fed by a series of 1 and 0. and are complementary, and SET (S) and RESET (R) inputs. [3]

The JK flip-flop augments the behavior of the SR flip-flop (J=Set, K=Reset) by interpreting the S = R = 1 condition as a "flip" or toggle command. Specifically, the combination J = 1, K = 0 is a command to set the flip-flop; the combination J = 0, K = 1 is a command to reset the flip-flop; and the combination J = K = 1 is a command to toggle the flip-flop, i.e., change its output to the logical complement of its current value. Setting J = K = 0 does NOT result in a D flip-flop, but rather, will hold the current state. To synthesize a D flip-flop, simply set K equal to the complement of J. The JK flip-flop is, therefore, a universal flip-flop because it can be configured to work as an SR flip-flop, a D flip-flop, or a T flip-flop. NOTE: The flip flop is positive edge triggered (Clock Pulse) as seen in the timing diagram.

The characteristic equation of the JK flip-flop is:

and the corresponding truth table is:

| JK Flip Flop operation [1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| Characteristic table | Excitation table | |||||||

| J | K | Qnext | Comment | Q | Qnext | J | K | Comment |

| 0 | 0 | hold state | 0 | 0 | 0 | X | No change | |

| 0 | 1 | reset | 0 | 1 | 1 | X | Set | |

| 1 | 0 | set | 1 | 0 | X | 1 | Reset | |

| 1 | 1 | toggle | 1 | 1 | X | 0 | No change | |

Note: The origin of the name for the JK flip-flop is detailed by P. L. Lindley, a JPL engineer, in a letter to EDN, an electronics design magazine. The letter is dated June 13, 1968, and was published in the August edition of the newsletter. In the letter, Mr. Lindley explains that he heard the story of the JK flip-flop from Dr. Eldred Nelson, who is responsible for coining the term while working at Hughes Aircraft. Flip-flops in use at Hughes at the time were all of the type that came to be known as J-K. In designing a logical system, Dr. Nelson assigned letters to flip-flop inputs as follows: #1: A & B, #2: C & D, #3: E & F, #4: G & H, #5: J & K.

Another theory holds that the set and reset inputs were given the symbols "J" and "K" after one of the engineers that helped design the J-K flip-flop, Jack Kilby.

References

[edit | edit source]- ↑ a b c Mano, M. Morris (2004). Logic and Computer Design Fundamentals, 3rd Edition. Upper Saddle River, NJ, USA: Pearson Education International. pp. pg283. ISBN 0-13-1911651.

{{cite book}}:|pages=has extra text (help); Unknown parameter|coauthors=ignored (|author=suggested) (help) - ↑ The D Flip-Flop

- ↑ D.A.Godse, A.P.Godse Logic Design ISBN 9788184312768